CAPÍTULO 4 LAS INSTRUCCIONES DE COMPROBACIÓN, BIFURCACIÓN Y SALTO

4.0 LA SECUENCIA DEL PROGRAMA

En todas las discusiones hasta ahora, se ha hablado poco cerca de cómo el microprocesador entiende las instrucciones utilizadas para

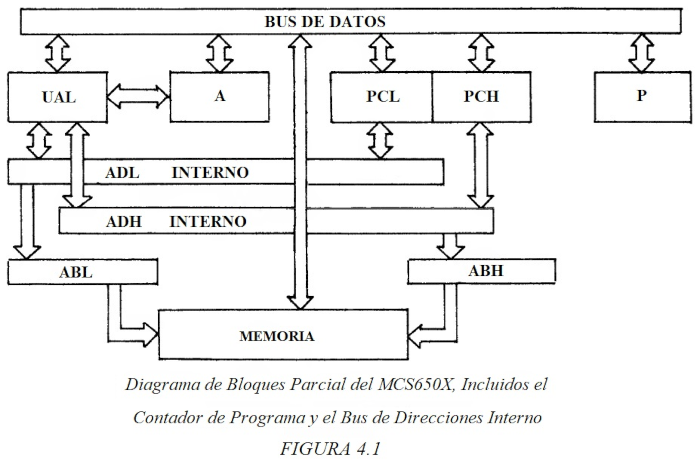

realizar varias manipulaciones aritméticas y del acumulador. De todas maneras, es apropiado que se desarrolle el concepto de programa y la forma en que el microprocesador determina cada instrucción. Para tal efecto se necesitan más registros en la máquina, tal como se muestra en la siguiente figura.

Aunque se han agregado dos registros de 8 bits, son los únicos registros en la máquina que actúan como si fueran un registro de 16 bits. Implementan un concepto conocido como conteo de programa o secuencia de programa y posteriormente su valor se denominará Contador de Programa (PC - Program Count). En determinadas operaciones puede ser conveniente hablar acerca de cómo son afectados el PCL (Program Count Low - Contador de Programa, byte de orden inferior), que es el registro inferior de 8 bits, o el PCH (Program Count High - Contador de Programa, byte de orden superior) que es el registro superior de 8 bits. La razón por la que este registro tiene 16 bits de longitud es que, si tuviera sólo 8 bits, podría hacer referencia solamente a un total de 256 ubicaciones. Dado que se accede a la Memoria a través del bus de Direcciones, el Contador de Programa, que es el que define la ubicación direccionable, debe tener el largo de una palabra.

El acceso a una posición de Memoria se denomina "direccionamiento". Corresponde la selección de una palabra de datos de ocho bits (byte) de entre un total de 65.536 posibles posiciones de Memoria. Esta selección se transmite a la Memoria a través de las 16 líneas de dirección (ADH, ADL) del microprocesador.

Para una discusión más detallada acerca de cómo un byte de memoria individual es seleccionado por las líneas de dirección, se remite al lector al Capítulo 1 del Manual de Hardware.

Si el Contador de Programa fuera de sólo 1 byte de largo, y si el patrón de bits que permite al microprocesador elegir la siguiente instrucción estuviera contenido en un byte de datos, sólo podríamos tener 256 pasos de programa. Aunque una máquina con estas características podría ser un juguete interesante, no tendría ningun valor real práctico.

Por lo tanto, casi todos los microprocesadores de 8 bits de la competencia han optado por tener un Contador de Programa de doble longitud. Aunque algunos de los microprocesadores de la familia MCS650X no tienen todas las líneas de dirección de salida necesarias para permitir que el usuario direccione 65K bytes de programa (debido a la restricción de número de pines del paquete), en todos los casos el Contador de Programa es capaz de direccionar 65K completos en virtud de sus 16 bits de longitud.

4.0.1 Uso del Contador de Programa para Obtener una Instrucción

El microprocesador contiene un contador de sincronización interna y de control de estado. Este contador, junto con una matriz de decodificación, gobierna el funcionamiento del microprocesador en cada ciclo de reloj. Cuando el estado del microprocesador indica que se necesita una nueva instrucción, se utiliza el Contador de Programa (puntero de dirección de programa) para elegir (direccionar) la siguiente ubicación de memoria3, y el valor que la memoria devuelve se decodifica para determinar qué operación de la familia MCS650X actuará a continuación.

3 Se usará ubicación o posición de memoria para referirse a la dirección de un byte en particular dentro de la memoria. (N. del T.)

Para usar el Contador de Programa y realizar esta operación correctamente, siempre se debe estar direccionando la operación que el usuario desea realizar a continuación. Esta operación puede ser una instrucción o pueden ser datos sobre los que operará la instrucción.

En la familia MCS650X, el Contador de Programa se configura con el valor de la dirección de una instrucción. A continuación, el microprocesador pone el valor del Contador de Programa en el bus de Direcciones, transfiriendo los 8 bits de datos de esa dirección de memoria al Decodificador de Instrucción. Luego, el Contador de Programa es incrementado automáticamente en uno y el microprocesador obtiene más datos para la operación de dirección necesaria para completar la instrucción. En el siguiente ejemplo:

Ejemplo 4.1: Acceder a las Instrucciones Usando el Valor del Contador P

| Contador P* | Contenido de la Ubicación |

|---|---|

| 0100** | LDA *Contador de Programa |

| 0101 | ADC **Notación Hexadecimal |

| 0102 | STA |

se puede ver cómo se utiliza el Contador de Programa para acceder a la secuencia de instrucciones para cargar A, sumar con acarreo y almacenar el resultado. En esto ejemplo, el Contador de Programa comienza en 0100. El microprocesador lee la ubicación 0100 usando el Contador de Programa para acceder a la memoria, y luego interpreta e implementa la instrucción LDA tal como se describió previamente. El Contador de Programa automáticamente se incrementa en uno en cada búsqueda de instrucción, pasando a 0101. Después de realizar el LDA, el microprocesador busca la siguiente instrucción, direccionando la memoria con el Contador de Programa. Esto recoge la instrucción ADC, luego se realiza la suma, y se utiliza el Contador de Programa que se ha incrementado a 0102 para buscar la siguiente instrucción, STA. Una vista simplificada de lo que realmente sucede dentro del microprocesador es que el Contador P es incrementado en 1 con cada instrucción.

Los procesadores de la familia MCS650X generalmente requieren más de un byte para interpretar correctamente una instrucción. El primer byte de una instrucción se llama OP CODE (CÓDIGO DE OPERACIÓN) y está codificado para contener una operación básica como LDA (Cargar en el Acumulador el contenido de una dirección de Memoria) y también los datos necesarios para permitir que el microprocesador interprete la dirección de los datos sobre los que se ejecutará la instrucción. En la mayoría de los casos, esta dirección aparece en la memoria justo a continuación, del byte del OP CODE. Esto permite que el microprocesador utilice el Contador de Programa para acceder tanto a la dirección, como al OP CODE.

El siguiente ejemplo muestra cómo el Contador de Programa recupera la instrucción y la dirección de los datos ubicada en la dirección 5155.

Ejemplo 4.2: Acceder al Direccionamiento de Datos Usando el Valor del Contador P

| Contador P | Contenido de la Ubicación |

|---|---|

| 0100 | LDA |

| 0101 | 55 |

| 0102 | 51 |

| 0103 | Siguiente Instrucción |

El OP CODE aparece en la dirección de memoria 0100. El 55 aparece a continuación, en la dirección 0101, el 51 en la dirección 0102, y el OP CODE para la siguiente instrucción aparece en la dirección 0103. En este ejemplo, vemos que el Contador de Programa se utiliza no sólo para recoger el código de operación LDA, sino que también se utiliza para recoger la dirección de memoria desde la que LDA obtendrá sus datos. En este caso, el Contador de Programa se incrementa automáticamente tres veces para recoger la instrucción completa, con el microprocesador interpretando en cada una de las búsquedas el dato apropiado. En otras palabras, la primera búsqueda se usa para obtener el OP CODE LDA, la segunda búsqueda se usa para obtener el byte de dirección de orden inferior de los datos y la tercera búsqueda se utiliza para obtener el byte de dirección de orden superior de los datos.

Esta es la forma en la que muchas de las instrucciones del microprocesador aparecerán, ya que se trata de la forma más sencilla de direccionamiento en la máquina y permite referenciar a cualquier posición de memoria.

Suponiendo que el microprocesador tiene la capacidad de iniciar el Contador de Programa en una instrucción conocida, debería ser bastante obvio que éste continuará avanzando desde esa ubicación hasta la máxima posición de memoria; luego pasará a la menor posición de memoria y seguirá subiendo por la memoria, obteniendo instrucciones y direcciones a medida que avanza. Esto nos dará un interesante programa secuencial, pero al que le falta un concepto tremendamente poderoso. El programa no tendrá la capacidad de realizar comprobaciones o implementar varias opciones basadas en los resultados de esas pruebas.

En el apartado anterior se desarrolló el concepto de banderas que se establecen en base al resultado de las operaciones del microprocesador.

Para usar estas banderas, el programa debe poder comprobarlas y luego cambiar la secuencia de operaciones que se están realizando dependiendo del resultado de la prueba.

El Contador de Programa emite continuamente una dirección, el microprocesador obtiene la instrucción almacenada en esa dirección y realiza operaciones en base a esa instrucción.

Para poder cambiar la secuencia de instrucciones ejecutadas por el microprocesador, el programador debe cambiar el valor del Contador de Programa. Como resultado, se incorporan las instrucciones de comprobación, las que resultan en un cambio en la secuencia del Contador de Programa como resultado de la realización de una de estas comprobaciones.

La forma más sencilla de cambiar la secuencia del programa es sustituir un nuevo valor en la ubicación del Contador de Programa. En los microprocesadores de la familia MCS650X, la forma más sencilla de cambiar la secuencia del Contador de Programa es por medio del uso de la instrucción JMP.

4.0.2 JMP-Saltar a una Nueva Posición de Memoria

En esta instrucción, el dato de la posición de memoria ubicado inmediatamente después del OP CODE es cargado en el byte de orden inferior del Contador de Programa (PCL) y el dato que viene a continuación, se carga en el byte de orden superior del Contador de Programa (PCH).

La notación simbólica para JMP es (PC + 1)→PCL, (PC + 2)→PCH.

Como se indicó anteriormente, "( )" significa "contenido de" una ubicación de memoria.

PC indica el contenido del Contador de Programa en el momento en que se obtiene el OP CODE. Por lo tanto (PC + 2)->PCH significa "el contenido del Contador de Programa más dos posiciones, contando desde la ubicación de obtención del OP CODE, es transferido al byte de orden superior del nuevo PC".

Cuenta con los modos de direccionamiento Absoluto y Absoluto Indirecto. La instrucción JMP no afecta a las banderas, sólo a PCL y PCH. La instrucción JMP permite utilizar el Contador de Programa para acceder a su nuevo valor tal como se ilustra en el siguiente ejemplo:

Ejemplo 4.3: Uso de la Instrucción JMP (En Modo de Direccionamiento Absoluto)

| Dirección | Datos | Comentarios |

|---|---|---|

| 0100 | JMP | Saltar a la Ubicación 3625 |

| 0101 | 25 | (Nuevo byte PCL) |

| 0102 | 36 | (Nuevo byte PCH) |

| 3625 | OP CODE | Siguiente Instrucción |

El Contador de Programa en el ejemplo comienza en la ubicación 100. El microprocesador carga una instrucción de salto. El Contador de Programa automáticamente se incrementa a 101, donde el microprocesador recoge y almacena temporalmente el 25. El Contador de Programa incrementa automáticamente a 102, donde el microprocesador recoge el 36.

El 3625 sustituye al Contador de Programa y se utiliza para buscar la siguiente instrucción. Por lo tanto, la instrucción JMP contiene dentro de su dirección la ubicación del nuevo Contador de Programa.

Aunque el salto permite el cambio de secuencia del programa, lo hace sin realizar ninguna comprobación. Entonces se trata de una instrucción JMP que se usa cuando se desea cambiar el Contador de Programa sin importar bajo qué condiciones.

Otro modo de direccionamiento de JMP es el Indirecto.

Antes de que se pueda entender esta técnica, se deben revisar las bases del direccionamiento Indirecto que se encuentran en el Capítulo 6. La instrucción JMP Indirecta se detalla en el Capítulo 9, página 141.

4.1 Bifurcación

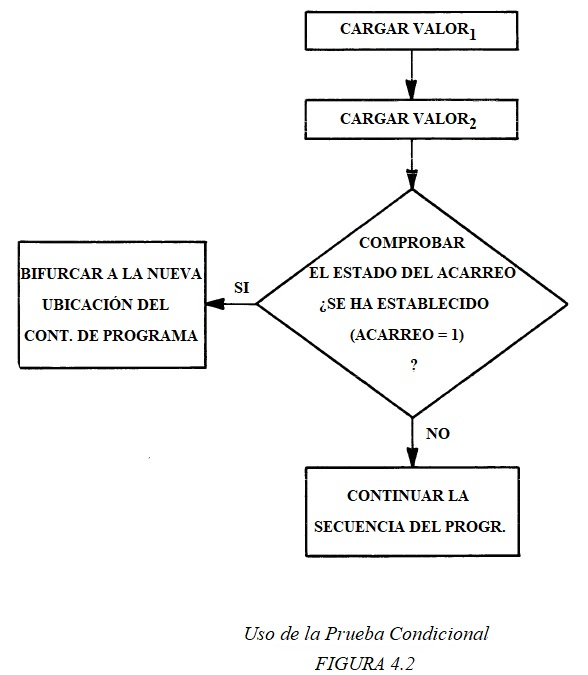

Para permitir el cambio condicional de la secuencia del programa, disponemos de una serie de instrucciones de bifurcación que comprueban y realizan cambios opcionales al Contador de Programa basado en el estado de las banderas. Para realizar un cambio condicional de secuencia, el microprocesador debe interpretar la instrucción, comprobar el valor de una bandera, y luego cambiar el Contador P si el valor corresponde a una instrucción. Si la condición no se cumple, el Contador de Programa sigue incrementándose de manera normal. La Figura 4.2 ilustra cómo se puede usar una prueba condicional.

En este ejemplo, se ve que la generación de un acarreo por parte de una operación de suma permitirá una bifurcación fuera de la secuencia hacia una nueva ubicación.

4.1.1 El Direccionamiento Relativo

Si se considera que la instrucción JMP requiere tres bytes, uno para el OP CODE, otro para el byte de orden inferior del nuevo Contador de Programa (PCL) y otro para el byte de orden superior del nuevo Contador de Programa (PCH), se puede apreciar que la bifurcación que se produce cuando se establece el acarreo también requeriría tres bytes. Debido a que la mayoría de los programas de control requieren muchos saltos o bifurcaciones continuas, la familia MCS650X utiliza el direccionamiento "Relativo" para todas las instrucciones de prueba condicional. Para realizar cualquier bifurcación, el Contador de Programa debe ser cambiado. Sin embargo, en el caso del direccionamiento Relativo, sumamos al Contador de Programa el valor que se encuentra en la posición de memoria que sigue al OP CODE. Esto nos permite especificar una nueva ubicación al Contador de Programa utilizando sólo dos bytes, uno para el OP CODE y uno para el valor a sumar. Para ilustrar esto, en el siguiente ejemplo, la instrucción "BCS (Branch on Carry Set) - Bifurcar si se establece el Acarreo" va seguida del valor 50. Si se establece en 1 la bandera de Acarreo, la nueva ubicación del programa será 108 + 50 = 158; en otras palabras, tomará la bifurcación.

Ejemplo 4.4: Ilustración de "Bifurcar si Se Establece la Bandera de Acarreo"

| Dirección | Datos | Comentarios |

|---|---|---|

| 0100 | LDA | Cargar el Primer Valor |

| 0101 | ADL1 | Byte Inferior del Primer Número |

| 0102 | ADH1 | Byte Superior del Primer Número |

| 0103 | ADC | Sumar el Segundo Valor |

| 0104 | ADL2 | Byte Inferior del Segundo Número |

| 0105 | ADH2 | Byte Superior del Segundo Número |

| 0106 | BCS | Comprobar si se Estableció la Bandera de Acarreo. Si Este Es el Caso, Bifurcar a la Dirección 0158 |

| 0107 | +50 | |

| 0108 | STA | De lo Contrario, Almacenar el Resultado de la Suma |

| 0109 | ADL3 | Byte Inferior del Tercer Número |

| 010A | ADH3 | Byte Superior del Tercer Número |

| 0158 | OP CODE | Nueva Instrucción |

El 0108 representa el valor del Contador de Programa después de leer el valor de desplazamiento (offset). El Contador de Programa aumenta automáticamente para que pueda hacer referencia a la siguiente ubicación de memoria en el próximo ciclo. La suma del desplazamiento es una suma binaria con signo, tal como se explica en la sección de aritmética. La bifurcación positiva se indica mediante un 0 en el bit 7 del valor relativo, y la bifurcación negativa está en forma de complemento a dos y se indica mediante un 1 en el bit 7. Las capacidades inherentes de este sistema de notación permiten una bifurcación condicional hacia adelante de 127 bytes contando desde la siguiente instrucción, y hacia atrás de 128 bytes contando desde esa instrucción. Todas las bifurcaciones de la serie MCS650X son bifurcaciones relativas condicionales y todas tienen la forma que se muestra arriba. La ventaja del direccionamiento Relativo se muestra mejor en el siguiente ejemplo:

Ejemplo 4.5: Secuenciación de Dos Instrucciones de Salto

| Dirección | Datos | Comentarios |

|---|---|---|

| 0100 | LDA | Cargar el Primer Valor |

| 0101 | ADL1 | |

| 0102 | ADH1 | |

| 0103 | ADC | Sumar el Segundo Valor |

| 0104 | ADL2 | |

| 0105 | ADH2 | |

| 0106 | BCS | Comprobar Si Se Estableció el Bit de Acarreo. Si Es Así, Saltar a la Dirección 0158 |

| 0107 | +50 | |

| 0108 | BMI | Comprobar Si Se Trata de un Número Negativo. Si Es Así, Saltar a la Dirección 0095 |

| 0109 | -75 | |

| 010A | STA | De lo contrario, Almacenar |

| 010B | ADL3 | |

| 010C | ADH3 |

En este ejemplo, se modificó el ejemplo anterior de una sola bifurcación para que adicionalmente se compruebe si el número resultante es o no negativo. Al secuenciar dos instrucciones de bifurcación, este ciclo es 2 bytes más corto debido al uso de saltos relativos en comparación con las instrucciones de bifurcación de 3 bytes.

4.1.2 Las Instrucciones de Bifurcación

4.1.2.1 BMI-Bifurcar Si el Resultado es Negativo

Esta instrucción toma el salto condicional si se ha establecido en 1 la bandera Negativo. BMI no afecta ninguna de las banderas o cualquier otra parte de la máquina a excepción del Contador de Programa, y sólo si el bit N está activo (N = 1).

El modo de direccionamiento de BMI es Relativo.

4.1.2.2 BPL-Bifurcar Si el Resultado es Positivo

Esta instrucción es complementaria a BMI. Es un salto condicional que toma la bifurcación cuando se borra la bandera Negativo. BPL se utiliza para comprobar si el bit 7 del último resultado fue borrado, en cambio BMI se utiliza para determinar si el último resultado fue negativo o si el bit 7 fue establecido en 1.

Esta instrucción no afecta a ninguna de las banderas ni otros registros, sólo afecta al Contador P cuando se borra la bandera Negativo.

El modo de direccionamiento de BPL es Relativo.

4.1.2.3 BCC-Bifurcar Si la Bandera de Acarreo ( C ) es igual a 0

Esta instrucción comprueba el estado de la bandera de Acarreo, y si ésta fue borrada, toma el salto condicional.

BCC no afecta a las banderas ni a otros registros, excepto el Contador de Programa, y sólo cuando se borra la bandera de Acarreo.

El modo de direccionamiento de BCC es Relativo.

4.1.2.4 BCS-Bifurcar Si la Bandera de Acarreo ( C ) es igual a 1

Esta instrucción toma el salto condicional si se ha establecido en 1 la bandera de Acarreo.

BCS no afecta a las banderas ni a otros registros, excepto el Contador de Programa, y sólo cuando se establece la bandera de Acarreo.

Su modo de direccionamiento es Relativo.

4.1.2.5 BEQ-Bifurcar Si el Resultado es igual a 0

Esta instrucción también podría llamarse "Branch on Equal - Bifurcar si es igual".

Esta instrucción toma el salto condicional cada vez que la bandera Z es establecida en 1, o si el último resultado es igual a 0.

BEQ no afecta a las banderas ni a otros registros, excepto el Contador de Programa, y sólo cuando se establece en 1 la bandera Cero.

Su modo de direccionamiento es Relativo.

4.1.2.6 BNE-Bifurcar Si el Resultado es distinto de 0

Esta instrucción también podría llamarse "Branch on Not Equal - Bifurcar si es distinto".

Comprueba la bandera Z y toma el salto condicional si la bandera Z fue borrada, lo que indica que el resultado anterior es distinto de cero.

BNE no afecta a las banderas ni a otros registros, excepto el Contador de Programa, y sólo cuando se borra la bandera Z.

Su modo de direccionamiento es Relativo.

4.1.2.7 BVS-Bifurcar Si la Bandera de Desbordamiento (V) es igual a 1

Esta instrucción comprueba la bandera V y toma el salto condicional sólo cuando ésta se establece en 1.

BVS no afecta a las banderas ni a otros registros, excepto al Contador de Programa, y sólo cuando se establece la bandera de Desbordamiento.

Su modo de direccionamiento es Relativo.

4.1.2.8 BVC-Bifurcar Si la Bandera de Desbordamiento (V) es igual a 0

Esta instrucción comprueba el estado de la bandera V y toma el salto condicional sólo cuando ésta se borra.

BVC no afecta a las banderas ni a otros registros, excepto el Contador de Programa, y sólo cuando se borra la bandera de Desbordamiento.

Su modo de direccionamiento es Relativo.

4.1.3 Resumen de las Bifurcaciones

En resumen, las bifurcaciones en la familia MCS650X tienen dos características: cada una de ellas comprueba el estado de una bandera y luego accede a la siguiente instrucción en la secuencia del programa si la bandera no cumple con el estado a comprobar, o suma el valor de desplazamiento al valor del PC en el OP CODE de la siguiente instrucción (PC + 1) para permitir que el programa cambie su operación. Esto permite al programador tomar decisiones a plena capacidad. Al escribir una secuencia de instrucciones de bifurcación, se puede determinar cualquier combinación de condiciones del microprocesador y tomar una nueva acción como resultado de las comprobaciones.

Se tienen cuatro condiciones de salto en los microprocesadores del MCS6501 al MCS6505. Estas son: salto en bandera de Acarreo, salto en bandera de Desbordamiento, salto en bandera N y salto en bandera Cero. Cada una de estas bifurcaciones toma un salto al establecer o al borrar la bandera correspondiente.

4.1.4 Solución a la Bifurcación Fuera de Rango

La instrucción de salto relativa es diferente a la instrucción de salto que puede llegar a cualquier lugar en la memoria, ya que el salto relativo está limitado a +127 bytes o -128 bytes a partir de la ubicación actual del Contador de Programa. Aunque para muchos ciclos y muchas pruebas este rango es suficiente, los programas más largos ocasionalmente tendrán la necesidad de saltar condicionalmente a una ubicación que se encuentra significativamente más allá del alcance directo del comando de salto. Este es uno de los usos de las bifurcaciones complementarias. Si un programa necesita saltar a una ubicación que se encuentra significativamente más lejos de 127, la siguiente solución facilitaría el salto:

Ejemplo 4.6: Uso de JMP para Saltar Fuera del Rango

| Dirección | Datos | Comentarios | |

|---|---|---|---|

| 100 | LDA | Cargar el Primer Valor | |

| 101 | ADL1 | ||

| 102 | ADH1 | ||

| 103 | ADC | Sumar el Segundo Valor | |

| 104 | ADL2 | ||

| 105 | ADH2 | ||

| 106 | BCC | Si No Hay Acarreo, Saltar Hacia Adelante 3 Posiciones (A Punto 2) | |

| 107 | +3 | ||

| 108 | JMP | Si Se Establece El Acarreo, Saltar a la Ubicación Especificada por ADH4, ADL4 | |

| 109 | ADL4 | ||

| 10A | ADH4 | ||

| Punto 2 | 10B | BMI | Comprobar si es Negativo |

| 10C | Offset | ||

| 10D | STA | ||

| 10E | ADL3 | Si No es Negativo, Almacenar el Resultado | |

| 10F | ADH3 |

En este ejemplo, se comprueba si se estableció el acarreo. Cuando el comando de salto necesita llegar más allá del rango de 128 posiciones de memoria, se requiere el uso de una bifurcación complementaria. En lugar de saltar a la posición usando "branch on carry set - bifurcar si se establece el Acarreo", se usa el comando "branch on carry clear - bifurcar si se borra el Acarreo" (una instrucción complementaria) que bifurca más allá de la instrucción JMP. Si no se toma la bifurcación complementaria, la instrucción JMP equivaldrá a la instrucción "branch on carry set - bifurcar si se establece el acarreo".

Esta técnica de saltar más allá de JMP usando una bifurcación complementaria es una solución universal al problema de la bifurcación fuera de rango.

Otra solución es encontrar una bifurcación similar a la ubicación que se encuentra dentro del rango y aunque esto involucra dos bifurcaciones para transferir el control, nos ahorra ubicaciones de memoria.

Por medio del uso del salto relativo se logra utilizar menos bytes de código que si se hubiera utilizado un salto condicional. Sin embargo, en programas grandes, la bifurcación fuera de rango ocurre con mayor frecuencia. Si el usuario puede determinar que una bifurcación estará fuera del alcance, debe usar la solución de salto en el momento en que está escribiendo el código. De lo contrario, varios ensambladores indicarán una bifurcación fuera de rango, lo que requerirá cambiar el código.

Nota :

La solución de salto hace que se sustituyan 5 bytes de código por 2 bytes de salto, el que en un ensamblador simbólico puede obligar a otras bifurcaciones a salir del rango. Esto podría causar varios ensamblajes consecutivos, pero esta técnica finalmente resolverá el problema.4.2 INSTRUCCIONES DE COMPROBACIÓN

Aunque la mayoría de las operaciones normales del microprocesador involucran el establecimiento de banderas, hay instrucciones específicas que están diseñadas sólo para establecer banderas y comprobarlas con la instrucción de bifurcación.

4.2.1 CMP-Comparar el Contenido de una Dirección de Memoria con el Acumulador

Esta instrucción resta el contenido de la Memoria al contenido del Acumulador.

Su notación simbólica es A - M.

El uso de CMP afecta a las siguientes banderas: La bandera Z es establece cuando la comparación da igual, y se borra de lo contrario; la bandera N se establece o se borra dependiendo del bit 7 del resultado; la bandera de Acarreo se establece cuando el valor en la Memoria es menor o igual al del Acumulador, y se borra cuando es mayor. El Acumulador no se ve afectado.

Es una instrucción de "Grupo Uno" y, por lo tanto dispone de los siguientes modos de direccionamiento: Inmediato; Página Cero; Página Cero, X; Absoluto; Absoluto, X; Absoluto, Y; (Indirecto, X); (Indirecto), Y.

El propósito de esta instrucción es permitirle al usuario comparar un valor en la memoria con el Acumulador, sin cambiar el valor del Acumulador. Un ejemplo donde esto se vuelve extremadamente importante es cuando se están recibiendo instrucciones de comandos desde un dispositivo externo. En este caso, un byte de entrada puede tener varios valores. Cada valor puede hacer que el programa realice una operación diferente. La única manera rápida de determinar el valor de los datos de entrada consiste en comparar la Memoria con una serie de constantes. Realizar operaciones de "comparación con constante" es bastante simple. Mediante el uso del modo de direccionamiento inmediato que se desarrollará más adelante, el siguiente ejemplo compara una entrada con tres valores y salta a diferentes ubicaciones en cada caso:

Ejemplo 4.7: Uso de la Instrucción CMP

| Datos | Comentarios |

|---|---|

| LDA | Cargar Valor |

| ADL | Byte Inferior de la Dirección |

| ADH | Byte Superior de la Dirección |

| CMP | Comparar COUNT 1 con el Acumulador |

| COUNT 1 | |

| BEQ | Si es Igual, Tomar la Bifurcación OFFSET 1 |

| OFFSET 1 | |

| CMP | Comparar COUNT 2 con el Acumulador |

| COUNT 2 | |

| BEQ | Si es Igual, Tomar la Bifurcación OFFSET 2 |

| OFFSET 2 | |

| CMP | Comparar COUNT 3 con el Acumulador |

| COUNT 3 | |

| BEQ | Si es Igual, Tomar la Bifurcación OFFSET 3 |

| OFFSET 3 | |

| Siguiente Instrucción | De lo Contrario, Vaya a la Siguiente Instrucción Basado en el Valor Predeterminado (COUNT 4). |

Este ejemplo muestra cómo utilizar la opción predeterminada. Un valor se compara contra 3 valores y si no coincide con ninguno, se asume un cuarto valor, o valor por defecto. Esta es una técnica útil para minimización de código.

La instrucción está diseñada para permitir una comparación entre 2 valores con signo, suponiendo que se hace un uso apropiado de las banderas Z, N y C. Para dar máxima flexibilidad, la instrucción realiza una resta efectiva entre el valor en la Memoria y el Acumulador. Esta es una resta efectiva porque le permite al usuario comparar si es igual o menor con una sola instrucción.

Los resultados de una comparación son:

| Comparación | N | C | Z | V |

|---|---|---|---|---|

| Acumulador < Memoria | Cualquiera | Borrar | Borrar | Sin cambios |

| Acumulador = Memoria | Borrar | Establecer | Establecer | Sin cambios |

| Acumulador > Memoria | Cualquiera | Establecer | Borrar | Sin cambios |

Entonces, para verificar si el Acumulador es menor que la Memoria, la comparación es seguida por un BCC; para comprobar si es igual, va seguido de un BEQ; y para comprobar si es mayor, le sigue un BEQ seguido de un BCS. Mayor o igual es verificado por BCS.

4.2.2 Comparación de Bits

La instrucción de comparación está diseñada para casos en los que el byte o múltiples bytes de un valor son comparados; Sin embargo, en el análisis de funciones lógicas, a menudo es necesario determinar la condición de un solo bit. Una de las formas de lograr esto es por medio del uso de la instrucción AND, tal como se discutió anteriormente. En otras palabras, el usuario puede cargar un valor en el Acumulador y hacer un AND con un campo que contiene un sólo bit en la posición de bit correspondiente al bit a comprobar. Se puede comprobar el estado del bit en la memoria mediante el uso del "salto en bandera Cero" luego del comando AND. Sin embargo, el uso de esta técnica implica destruir el valor del Acumulador con la instrucción AND. Por lo tanto, el buscar en una tabla un sólo bit en una posición determinada necesita la recarga del valor de prueba (máscara) después de cada instrucción AND.

La instrucción BIT se usa para permitir el muestreo de Memoria sin cambiar el Acumulador.

4.2.2.1 BIT-Comparar los Bits del Contenido de una Dirección de Memoria con los del Acumulador

Esta instrucción realiza un AND entre una posición de Memoria y el Acumulador, pero no almacena el resultado del AND en el Acumulador

La notación simbólica es M^A.

La instrucción BIT afecta la bandera N: se le asigna el valor del bit 7 de la Memoria que se está probando; afecta a la bandera V, se le asigna el bit 6 de la Memoria que se está probando; y afecta a la bandera Z: esta se establece en 1 si la operación AND entre el Acumulador y la Memoria es igual a cero, de lo contrario Z se borra. No afecta al Acumulador.

Sus modos de direccionamiento son Página Cero y Absoluto.

La instrucción BIT en realidad combina dos instrucciones del PDP-11 y del MC6800: las instrucciones TST (Test Memory) y BIT (BIT Test). Esto permite, como la prueba de comparación, el examinar un bit individual sin alterar el valor en el Acumulador. Esto se ilustra en el siguiente ejemplo:

Ejemplo 4.8: Programa de Muestra Utilizando la Instrucción de Comparación BIT

| Datos | Comentarios |

|---|---|

| LDA | Cargar MASK en el Acumulador |

| MASK | |

| BIT | Comprobar Primer Valor de Memoria Para el Bit de MASK |

| ADL1 | |

| ADH1 | |

| BNE | Bifurcar si se Establece |

| +50 | |

| BIT | Comprobar Segundo Valor de Memoria Para el Bit de MASK |

| ADL2 | |

| ADH2 | |

| BNE | Bifurcar si se Establece |

| -75 | |

| etc. |

En este ejemplo, el valor "MASK" cargado en el Acumulador es en realidad un título descriptivo, ya que, en este byte de 8 bits, sólo uno de ellos es igual a 1. El uso de este byte en la operación AND, inherente a la prueba del comando BIT, enmascarará efectivamente todos los bits en la ubicación de Memoria bajo prueba, excepto la posición del bit correspondiente al 1 que reside en el Acumulador. En el ejemplo 4.8, se realiza un AND entre el byte MASK y los datos que se encuentran en la ubicación ADH1, ADL1; y si el bit bajo prueba es un 1, se tomará la bifurcación; si no es un 1, se probará la segunda ubicación de Memoria con la misma máscara, y así sucesivamente.

En la familia de microprocesador MCS650X se han realizado dos modificaciones a la versión PDP-11 de esta instrucción: Además de la característica no destructiva del comando BIT que nos permite aislar un bit individual mediante el uso de la prueba "bifurcar si es igual" o "bifurcar si no es igual". Estas modificaciones nos permiten comprobar el bit 6 y el bit 7 del campo examinado con el comando BIT. Esta característica es particularmente útil para servir interrupciones sondeadas (polled interrupts) y particularmente al operar con el MCS6520 (Peripheral Inferface Device - Dispositivo de interfaz periférica). Este dispositivo tiene un bit de detección de interrupción en el bit 6 y el bit 7 de la palabra de Estado. Es un estándar del bus M6800 que siempre que sea posible, el bit 7 debe reflejar el estado de la interrupción de un dispositivo de E/S. Este significa que, en circunstancias normales, un análisis de la bandera N después de una instrucción de carga (LDA, LDX, LDY) o de la instrucción BIT debe indicar el estado del bit 7 en el dispositivo de E/S que se está muestreando. Para facilitar esta prueba usando la instrucción BIT, se asigna el bit 7 de la memoria que se está comprobando a la bandera N independientemente del valor almacenado en el Acumulador.

Esto es distinto a la instrucción BIT del M6800, que requiere que el bit 7 también sea establecido en el Acumulador para poder establecer la bandera N. La ventaja para el usuario es que, si decide comprobar el bit 7 en la memoria, lo puede hacer directamente comprobando la bandera N con una instrucción BIT seguido de una instrucción "bifurcar si es menor" o "bifurcar si es mayor". Esto significa que el muestreo de E/S se puede realizar en cualquier momento durante la operación de las instrucciones, independientemente del valor precargado en el Acumulador.

Otra característica de la comprobación usando BIT es la configuración del bit 6 en la bandera V. Como se indicó anteriormente, la bandera V normalmente está reservada para el desbordamiento en la posición del signo durante una instrucción de suma y resta. En otras palabras, la bandera V no se ve perturbada por las instrucciones típicas. Cuando se utiliza la instrucción BIT, se supone que el usuario está tratando de examinar la memoria que está comprobando con la instrucción BIT. Para obtener el valor máximo de la instrucción BIT, el bit 6 de la memoria que se está probando se almacena en la bandera V.

En el caso de una operación normal, el usuario debe organizar la memoria de manera tal que ambas banderas a ser comprobadas están en el bit 6 ó en el bit 7; si este es el caso, no es necesario cargar una máscara apropiada en el Acumulador antes de implementar la instrucción BIT. En el caso del circuito integrado MCS6520, la instrucción BIT se puede utilizar para interrumpir el muestreo, independiente de la máscara. Esto permite que el programador compruebe tanto el bit 6 como bit 7 del MCS6520 sin perturbar al Acumulador. En el caso de las interrupciones concurrentes, es decir, bit 6 y bit 7 ambos activados, el hecho que la bandera V se establezca automáticamente mediante la instrucción BIT le permite al usuario posponer la prueba del "sexto bit establecido" hasta que haya manejado totalmente la interrupción para el "bit 7 establecido" a menos que realice una operación aritmética después de la operación BIT.

Ir al siguiente capítulo